的增幅。而长久来看,半导体晶圆代工领域也是会总体保持增长。未来,芯片将越来越变得无处不在,价值慢慢的升高,重要性也慢慢变得高,在社会中逐渐变成引导社会变革的核心力量之一。

就此台积电中国区总经理罗镇球在ICCAD2023就表示:“整个半导体在2000年的时候全球产值做到了2000亿美金左右,2010年到了3000亿,今年肯定仍旧超过4000亿。我刚刚跟各位说明了半导体应用正在逐步铺开,现有半导体应用产品使用的半导体数量逐步在增加,我们可以非常乐观地预估,在2030年之前球半导体产业产值肯定可以超过1万亿美金,这是一个非常有希望的行业。”

然而,增长不会天上掉下来的馅饼,在增长的背后是无数科研人员的付出和企业中巨大的科研资金投入。以晶圆代工行业的龙头老大,台积电为例,台积电每年花300亿美金做资本支出,同时有超过8000位研发人员,在整个2023年台积电在研发领域就花费了超过55亿美元。

如此巨大的科研投资,台积电的研究力量主要专注于两个方向,一是2D的平面式微缩推进到3D的整合;二是提升芯片的高能效表现。

我们先来谈谈什么是“2D的平面式微缩推进到3D的整合”。当各位稍微了解一些前者,对于后者的疑问自然会迎刃而解。

1959年,MOSFET被发明,1963年CMOS被发明,从此更高的能效和更好的散热成了芯片设计,这门“新学科”永恒的话题。所谓微缩,顾名思义,就是晶体管尺寸的逐渐缩小。根据Dennard于1974年对CMOS缩放(CMOS scaling)原理进行的总结,结合摩尔定律为微电子行业提供了科学的缩放(scaling)方向。Dennard缩放原理指出:当晶体管尺寸缩小半时,晶体管的性能(如速度、功耗等)将会提升约一倍,同时保持电压不变。这意味着,通过不断缩小晶体管的尺寸,我们可以在同样的芯片面积内集成更多的晶体管从而提升芯片的性能。

而随着晶体管尺寸的不断缩小,其也带来了一些难题,一是控制精度和机械加工精度要达到纳米级别,目前随着先进光刻机的应用,晶体管的尺寸缩小已经逐渐达到瓶颈,而这种瓶颈还没有看到能完美突破方向;第二个难题则是芯片散热困难,线路密集会使芯片温度升高,会使微型器件失去正常的功能。而为了解决这些问题,芯片开始从2D到3D发展。

首先,我们先要了解一下,什么是芯片的“封装”。芯片从设计到生产再到消费者手中是个极其复杂的过程,设计公司做完逻辑和物理设计,将最终设计结果交给芯片代工厂。代工厂经过无数复杂的流程,最终会在一块大的晶圆上做出许许多多的小芯片。而这一个个的小芯片,则被称为“die”。为什么要叫这么一个不吉利的名字?有一种说法是说,早期芯片生产工艺水平不足,切割出的芯片良品率很低,经常就“die”了,因此,工程师们才给它取了这么一个自嘲的名字。而从这个“小道消息”中,各位读者应该能意识到,die非常非常脆弱,因此不能直接使用,需要再给它加上一层保护壳,而这个过程,就叫做“封装”。简单点说,封装技术需要将die固定在基板(substrate)上,然后将die上的引脚连接到芯片外壳的引脚上。

的引脚和基板连接(称之为‘键合’),最后把整个芯片封装起来,密封用的材料有塑料,陶瓷等。这种封装技术的优点是生产工艺相对简单,成本较低;缺点是封装完的芯片尺寸比

之后,随着技术的进步,又出现了“倒装”,即将die的正面朝下,提前做好焊点的技术,倒装的应用使得封装尺寸和芯片接近,并且有更多的引脚,但是随着芯片功能越来越多,I/O数量急剧增加,传统的封装已经难以满足要求。后来据此还衍生出了Fan-Out WLP(Wafer Level Packages),也叫FOWLP技术,但是文章篇幅有限,有兴趣的读者可以自行了解。

上文中所言都是单独die的封装,一颗完整的现代芯片,单个die是远远不够的,需要将多个die封装在一起,而这之中的封装方式便是2D,2.5D,3D封装。

最简单的办法,便是最简单的“2D封装”,即:将多颗die正面朝下,焊接到基板上,die与die之间的互连就靠基板上的走线。这种办法的缺点是基板上的布线密度低,因此die与die之间的互连受限。而为了解决布线密度的问题,芯片封装来到了2.5D阶段。

2.5D封装之中的代表就是台积电推出的CoWoS技术。台积电为了解决die和die之间的布线密度问题,在die和基板之间加入了一层“硅中介层”。Die和die之间并不直接连接,而是与中介层连接,也就是说硅中介层充当了die-die互连和die-substrate互连角色。由于中介层的布线可以直接使用半导体工艺制造,因此其布线密度得以大幅提升。这种技术的缺点也是十分明显,由于中介层也是使用半导体工艺制造,其成本很难下降,其面积也严重受到半导体工艺的限制,很难做大。

随后,为了降低这成本不低的中介层面积,英特尔发明了EMIB,将die-die的互连用“硅桥(Si Bridge)”实现,且硅桥嵌入在基板内部,die-substarte的连接通过传统方法实现。这种做法可以大大降低硅中介层的面积,减少成本,减轻多die封装的限制。

从上文中的描述中各位读者也许可以发现,无论是2D封装还是2.5D封装,所有的die都是在同一平面之内,所以,这也就注定了要想用更多的die,就要更大的封装面积,这对于需要小型化的芯片来说无疑是背道而驰,注定了一颗芯片中不能有太多die。那怎么办呢?工程师们给出了他们的解决方案:把die像大楼一样,垒起来!

从2D到3D,这就是一个很大的进步。2D到3D,包含晶体管的架构,从原来平坦式的晶体管,变成已经现在立体式晶体管。除了在芯片上的晶体管开始变成3D之外,封装部分也把它变成了3D。

在3D封装中,工程师们通过垂直堆叠芯片,用更短的互连和高带宽连接起来,进一步弥补了二维封装设计中的缺陷。在传统的2D封装中,往往需要大量远距离连线,电路中控制电容、电阻的充放电造成的信号延迟,即RC延时难以控制。为了提高信号传输速度,必须降低RC延迟,那么用3D封装的短程垂直互连来替代2D封装的长程互连是封装工艺技术向更高阶发展的必然趋势。

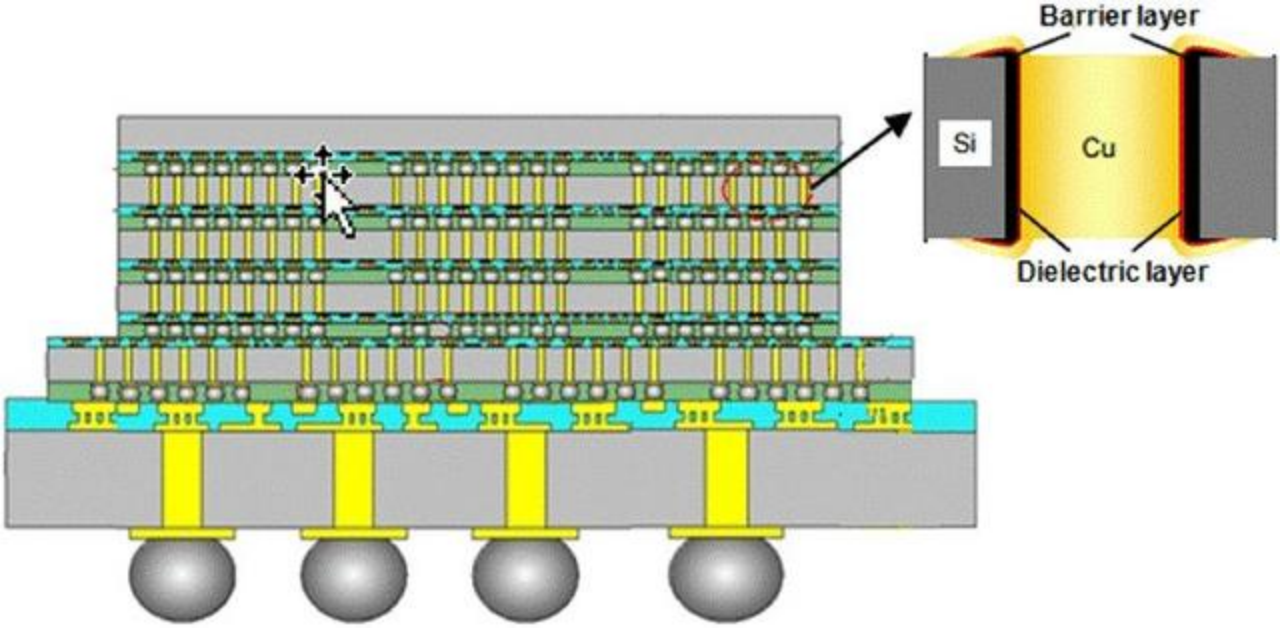

而实现在3D封装的关键技术就是TSV硅通孔技术。简单来讲,TSV技术通过在芯片与芯片之间、晶圆和晶圆之间制作垂直导通,通过导电物质的填充实现硅通孔的垂直电气互联,它是目前唯一能实现垂直电互联的技术。这种技术看上去十分完美,但是难度太高,成本太大。试想一下,在又薄又脆弱的玻璃片上打很多通孔,再把这些经过处理之后更加脆弱的芯片垒成“摩天大楼”,听着就十分困难。因此,TSV技术在1958年被威廉·肖特基(William Shockley)第一次申请专利之后,直到40多年后的21世纪才逐渐走向商用,2000年,日本分别率先研发出第一款三层堆叠的图像传感器和三层堆叠的存储器件。2005年,10层堆叠的存储芯片被研制出来。2007年集成TSV的CIS芯片由Toshiba公司量产商用,同年ST Microelectronics和Toshiba一起推出8层堆叠的NAND闪存芯片。2013年第一款HBM存储芯片由韩国Hynix推出。2015年,第一款集成HBM的GPU由AMD推出。

目前,所有的3D封装技术都是基于TSV技术之上,随着市场对于芯片算力要求的不断提高,和摩尔定律逐渐难以“遵守”的压力各大厂商纷纷推出自己的技术,比较有代表性的是台积电的SoIC技术和英特尔的Foveros技术。

SoIC(系统整合芯片)是一种基于台积电的CoWoS(Chip on wafer on Substrate)与多晶圆堆叠(WoW)封装技术开发的新一代创新封装技术。其采用TSV技术,可以达到无凸起的键合结构,它是业界第一个高密度3D小芯片堆叠技术,可将不同尺寸、功能、制程节点的芯粒异质整合。

SoIC技术 的主要特点是将有源和无源芯片集成到新的集成SoC系统中,该系统在电气上与本机SoC相同,以实现更好的外形尺寸和性能。这意味着SoIC技术可以实现更高效的芯片堆叠,从而提高了系统的性能和集成度。

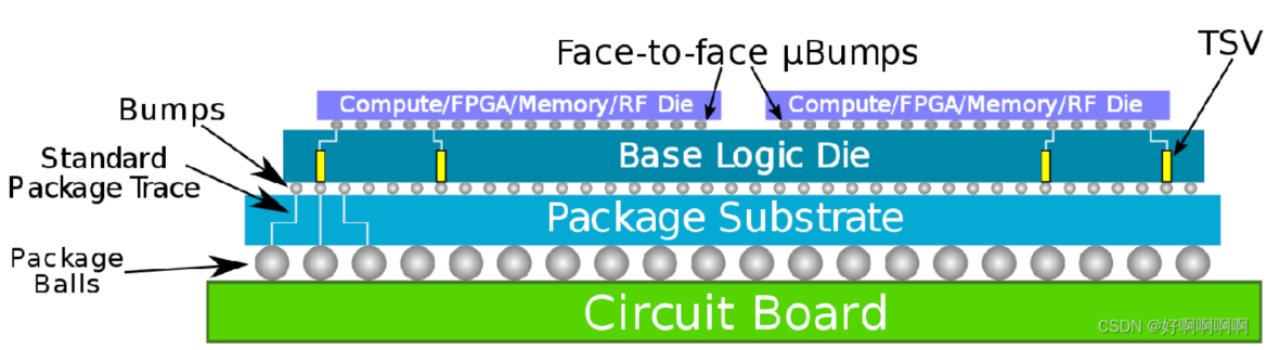

Foveros于2019年Intel首次推出,是一种先进的3D面对面芯片堆叠封装工艺技术。其在封装基底之上安放一个底层芯片,起到主动中介层的作用。在中介层里有大量的TSV 3D硅穿孔,负责联通上下的凸块,让上层芯片和模块与系统其他部分通信。

在Foveros技术中,一个基本的逻辑芯片位于底部,其顶部可以放置其他有源组件,如另一个逻辑芯片、存储器、FPGA,甚至模拟/射频芯片。这种技术使得多个芯片可以垂直堆叠,形成一个单一的、高度集成的系统。

Foveros的主要特点是通过极细间距的36微米微凸块(很可能是铜柱)进行面对面(F2F)芯片对芯片键合。这一特点使得Foveros技术在封装领域具有显著的优势。F2F的流程相对简单。对底部和顶部芯片进行凸块处理,然后进行背面研磨,最后进行分割。这种流程使得Foveros技术的生产效率较高,并且能够实现高精度的芯片对芯片键合。同时,F2F具有互连密度扩展和较低的电线寄生效应的优势。这意味着使用Foveros技术可以大大提高芯片之间的连接密度,同时减少电线的寄生效应,从而提高系统的性能和稳定性。这对于高性能的应用程序尤为重要。

芯片制造从最早的2D封装到现在的2.5D和3D封装,整体向着更强的性能和更低的功耗发展,总体上整个产业都向着台积电所努力的两个方向发展,即:2D的平面式微缩推进到3D的整合和提升芯片的高能效表现。我们谈完2D到3D的发展,各位读者就能发现:芯片设计的复杂度慢慢的升高,Fab(半导体制造厂)很多时候没有办法使用一些简单地电路设计就去评估不同的工艺选项,而必须越来越多地依赖Fabless(无晶圆厂半导体公司)客户的反馈来调整工艺。这就引出了一个全新的赛道——电路设计与工艺协同优化(design technology co-optimization,DTCO)

总的来说,DTCO是一个相当宽泛的概念,涵盖了任何将半导体工艺和具体电路设计进行协同优化的措施。简单来说,DTCO就是根据半导体芯片的具体要求去优化半导体工艺。

在DTCO的实践中,Fab在开发新一代工艺时,通常会使用一些常规的电路设计来评估各种新一代工艺中的选项,从而决定最佳方案。这种做法有助于确保工艺与电路设计的最佳协同。

Fab也会与合作的Fabless合作,提供早期评估版本的PDK(工艺设计套件)。Fabless使用PDK来设计一些关键电路并评估其性能,然后为Fab提供反馈,帮助Fab迭代工艺设计。这种合作模式有助于确保工艺与电路设计的紧密配合,从而实现最佳的性能和可靠性。

目前,随着半导体工艺的发展,摩尔定律的延续变得越来越具有挑战性,开发和使用新一代半导体工艺的成本越来越高,同时性能提升也越来越小。因此,借助DTCO来优化半导体工艺和电路设计变得越来越重要。未来,DTCO将进一步发展为STCO(System-Technology Co-Optimization),即在常规电路-工艺优化之外额外考虑2.5D/3D IC封装的协同优化。这种协同优化可以进一步改善芯片的性能和可靠性,同时降低成本。根据顶级半导体研究机构IMEC的分析,DTCO和STCO从10nm开始对于半导体工艺节点进一步演进起的作用越来越大,并逐渐取代之前摩尔定律中的简单减小工艺特征尺寸的模式。这在某种程度上预示着,通过DTCO和STCO的协同优化,可以实现更先进的半导体工艺和更高的性能。