做任何模块前,要确定输入输出端口有哪些,有一个整体的概念;方便以后模块调用;

2.2实操(quartus13.1与modelsim_alter的操作,主要是每次重新捡起来的时候,都要重新看一遍,所示汇总一次)

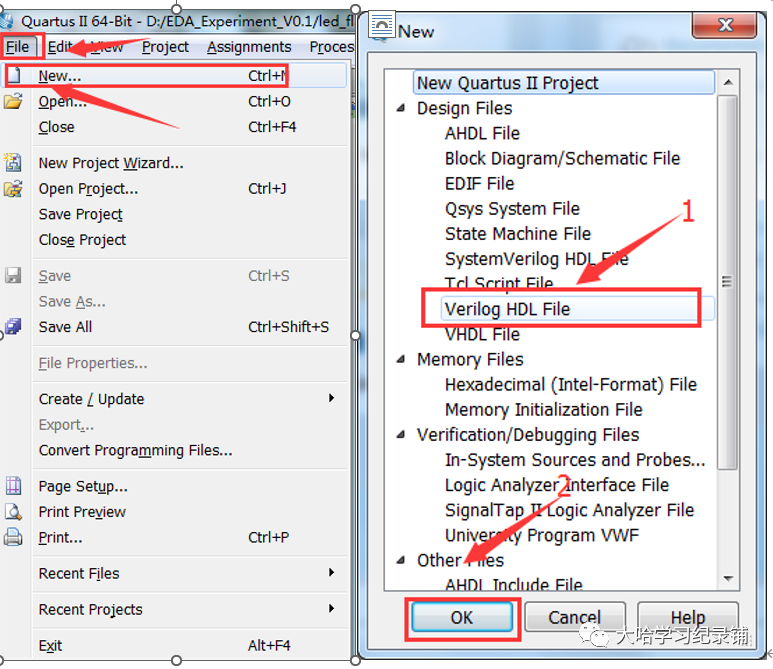

至此完成了工程的创建。下面我们就来创建工程顶层文件,我们大家可以点击菜单栏的 FileNew…,然后弹出如图所示的新建文件窗口, 在这里我们可以选择各种需要的设计文件格式。可以作为工程顶层设计文件的格式主要在 Design Files 类别下,我们选择VerilogHDL File并单击OK 完成文件创建。在主编辑窗口中, 出现了一个新建的空白的可编辑文件, 我们接着在该文件中输入实现实验功能的一段 Verilog 代码,并保存文件名为h_addr.v

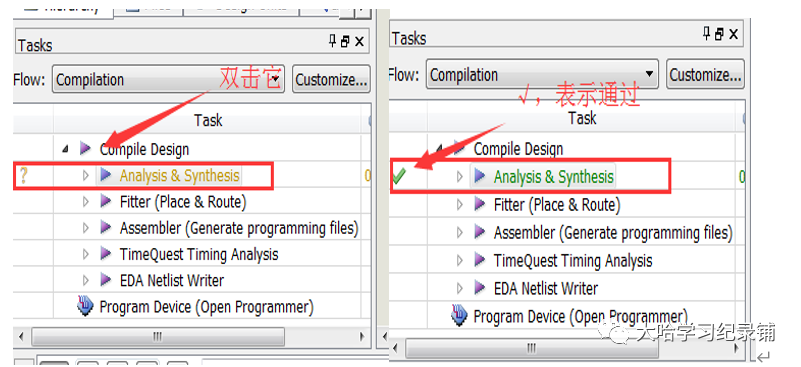

自此, 我们的工程创建和设计输入工作已经完成。但是为了验证一下设计输入的代码的基本语法是否正确,点击 Flow→Compilation 下的 Analysis & Elaboration 按钮,如图所示。同时我们大家可以输出打印窗口的 Processing 里的信息,包括各种 warning 和 Error。

Error是不得不关注的,因为 Error 意味着我们的代码有语法错误,后续的编译将无法继续;而warning 则不一定是致命的,但很多时候 warning 中暗藏玄机,很多潜在的问题都可以从这些条目中寻找到蛛丝马迹。当然了,也并不是说一个设计编译下来就不可以有 warning,如果能够确认这些 warning 符合我们的设计要求,那么可以忽略它。

最后,在 Analysis & Elaboration 完成后,通常前面的问号会变成勾号,表示通过。

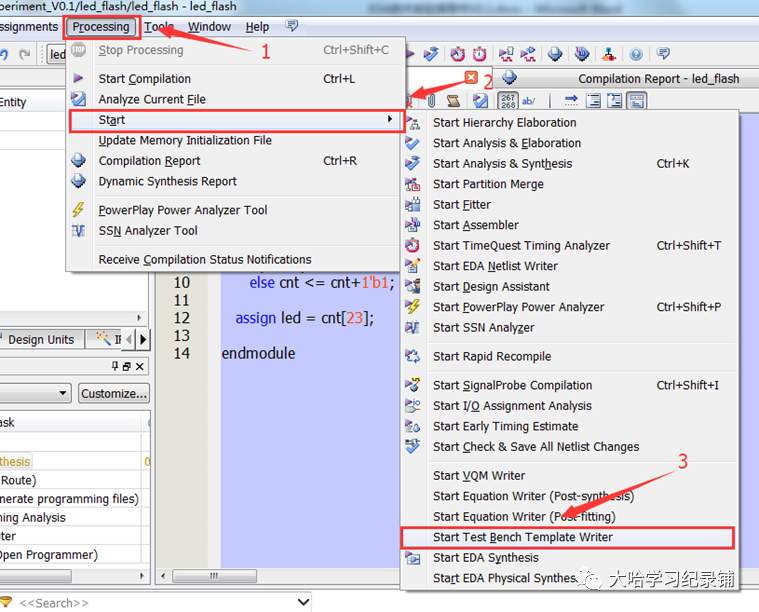

完成了前面基本的设计输入后, 为了进一步的验证代码所实现功能的正确性, 我们还需要进行仿真测试。首先我们点击菜单栏的Processing→Start→Start Test Bench Template Writer,随后弹出提示“Test Bench TemplateWriter was successful“,那么我们就已经创建了一个 Verilog测试脚本,在此脚本中,我们大家可以设计一些测试激励输入并且观察相应输出, 借此我们就能够验证原工程的设计代码是否符合要求。

我们大家可以在 Quartus II 中打开这一个文件,并且将其重新编辑(见2.1.3测试文本撰写)

运行,就不可以出波形,自己觉得是程序的事,但是就是找不出错误所在,请大家帮忙看看。。以下是

次阅读 --

桥逆变器拓扑如下: 电压环和电流环控制图如下: 调制方式如下:2.

次阅读 --

次阅读 --

次阅读 --

次阅读 --

系统 /

次阅读 --

前端系统的研究 /

相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级

次阅读 --

的区别? /

次阅读 --

和全加器的原理及区别(结构和功能) /

次阅读 --

是实现两个一位二进制数加法运算的电子器件,具有被加数A和加数B两个输入端、输出端Y,经常被应用在算数运算电路中,用于计算两个一位二进制相加,不考虑低位进位。

次阅读 --

真值表 /

次阅读 --

次阅读 --

设计 /

次阅读 --

电路的设计呢? /

可用于最低位求和,并给出进位数。第二位的相加有两个待加数和,还有一个来自前面低位送来的进位数。