NC, Phase Increase,频率操控字,用于生成希望频率的波形数据;

POFF, Phase Offset,相位操控字,用于生成希望初始相位的波形数据;

Spurious Free Dynamic Range (dB),无杂散动态规模,用于调整正弦和余弦输出数据的位宽,假定需求的正弦和余弦输出数据的位宽是16bit,动态规模的数值设置为16*6 = 96 ;

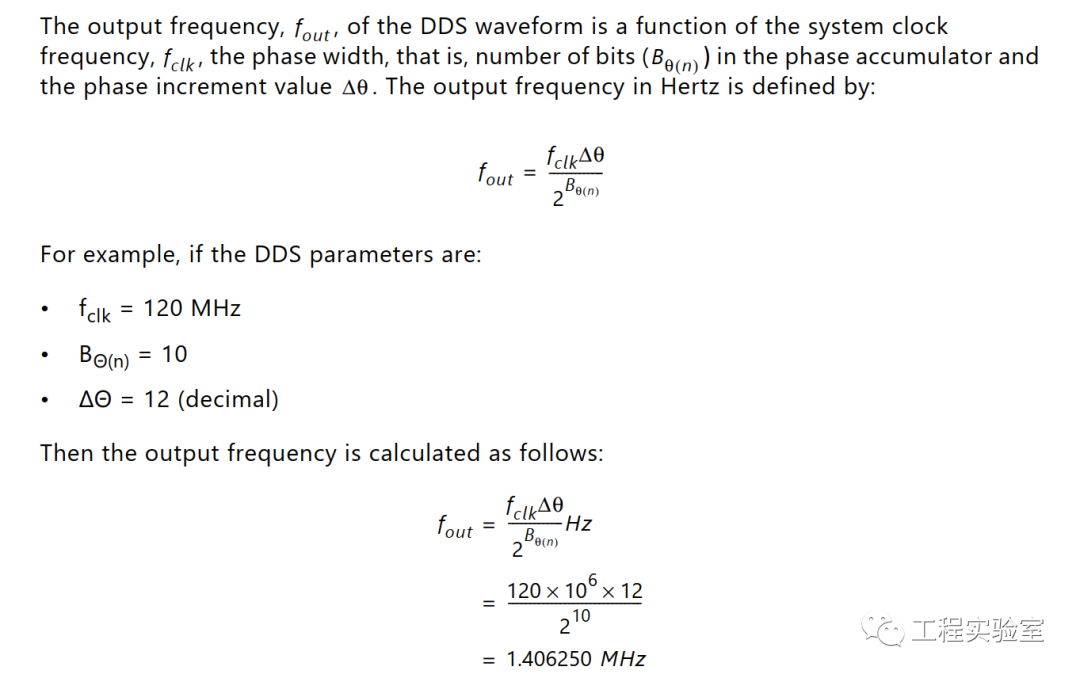

Frequency Resolution(Hz),频率分辨率,IP核输出正余弦信号能到达的最小频率。参阅时钟/采样时钟(f_clk)、频率操控字(delta_theta)、输出频率(f_out),三个变量之间的核算联系如下:

上述公式中2^n(公式中的分母),n取决于频率分辨率,分辨率越小,n的数值越大,频率操控字(delta_theta)的位宽越大。

假定体系的参阅时钟是f_clk=250MHz, 经过公式易知,频率操控字delta_theta的取值规模仍是0 ~ 2^n,对应输出信号的频率,其取值规模是0~f_clk。依据采样定理,所发生的信号频率不能超越时钟频率(采样时钟频率,250Mhz)的一半,在实践运用中,为了能够更好的确保信号的输出质量,输出频率不要高于时钟频率的33%,避免混叠或谐波落入有用输出频带内。

Fixed是固定相位增量,IP核运转过程中不行更改,即输出的信号频率固定不变;

Programmable可编程,可在DDS运转过程中随时写入频率操控字改动输出波形的频率,用于偶然改动频率;

输出信号假如勾选为正弦和余弦信号,输出信号的成果如下:高位bit31:16为正弦信号,低位bit15:0为余弦信号。

工程需求:参阅时钟是250MHz,运用8路DDS组成具有2G采样率的信号,输出到DAC芯片。

处理方案:参阅时钟是250MHz,周期为4ns,2G采样率的信号,采样周期为0.5ns,运用DDS-IP核输出250MHz的信号,相邻2个采样点之间的时刻距离是4ns,要满意2G采样率,原始4ns的周期内需求有8个采样点,DDS-IP核的信号输出经过移相完成,每个DDS-IP核移相的巨细为频率操控字的1/8。

2.4、仿线、单个DDS调制模块在运用的时分,假如输出频率高于选用时钟频率的一半时分,DDS输出信号会失真。比方设置输出频率超越时钟频率的一半(大于125Mhz),导致单个DDS输出信号失真。试验发现虽然单个DDS输出信号失线路DDS移相后输出)依旧能确保设置的信号频率,比方图2-3-3中单个DDS输出信号失真,可是组成后的信号仍然质量较高;

2、每个DDS-IP核移相的巨细为频率操控字的1/8,频率操控字的位宽为24bits,频率分辨率为100hz, 即整个DDS模块能够输出频率为100hz或许100hz整数倍的波形数据。频率操控字的位宽决议了频率分辨率的巨细,频率操控字的位宽越大,DDS输出信号的频率分辨率越小,体系输出信号的频率规模越宽。

图2-5-1 50Mhz正弦波信号,经过采样率为2G的DAC芯片输出模拟信号

图2-5-2 250Mhz正弦波信号,经过采样率为2G的DAC芯片输出模拟信号

` 本帖最后由 eehome 于 2013-1-5 09:56 修改 开关电源研制人员所需具有的

2:开发一个开关电源产品一切必要进行的各种优化和折中3:确保开关电源产品一次开发成功所需具有的工程本质开关电源

破解之后 仍是没有办法处理 可是我在Google上的找到一个处理办法便是把

试卷共享 /

详解 /

及修理水平 /

今日给我们带来一篇实战事例,本事例旨在运用之前学习的时刻序列剖析和猜测根底

带32位MCU和高精度ADC的SoC产品-SD93F系列开发攻略(九)

将苹果iPhone 4S 5S 6SP X XSMAX 12PROMAX一起开机 成果失算了 #吃拆玩呗